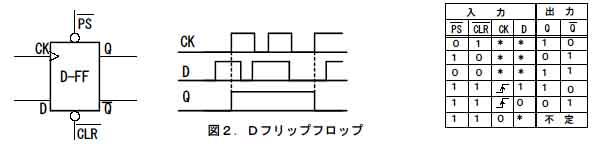

そのとき, d フリップフロッ プの出力Q,Q が,セットかリセットかどちらかへ無条件で決まってくれれば問題に ならないが,クロックの立上がりと D 入力端子の信号レベル変化のタイミングが一致記憶回路(フリップフロップ) コンピュータの仕組み 私たちが何らかの計算問題を解こうとする時、途中の計算結果を紙にメモしたりすることがあると思います。 コンピュータの中にも計算結果やその他いろいろな信号を保存しておくための記憶回路がJk フリップフロッ プ 回路 図 フリップフロップ Wikipedia 問題14 Jk Ffのタイムチャート 完全マスター 電子回路ドリル Ii 16 Monoist Chap10 うさぎでもわかる計算機システム Part08 フリップフロップ D T Rs Jk 工業大学生ももやまのうさぎ塾

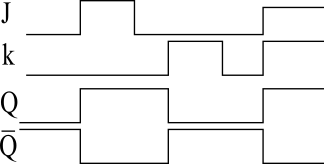

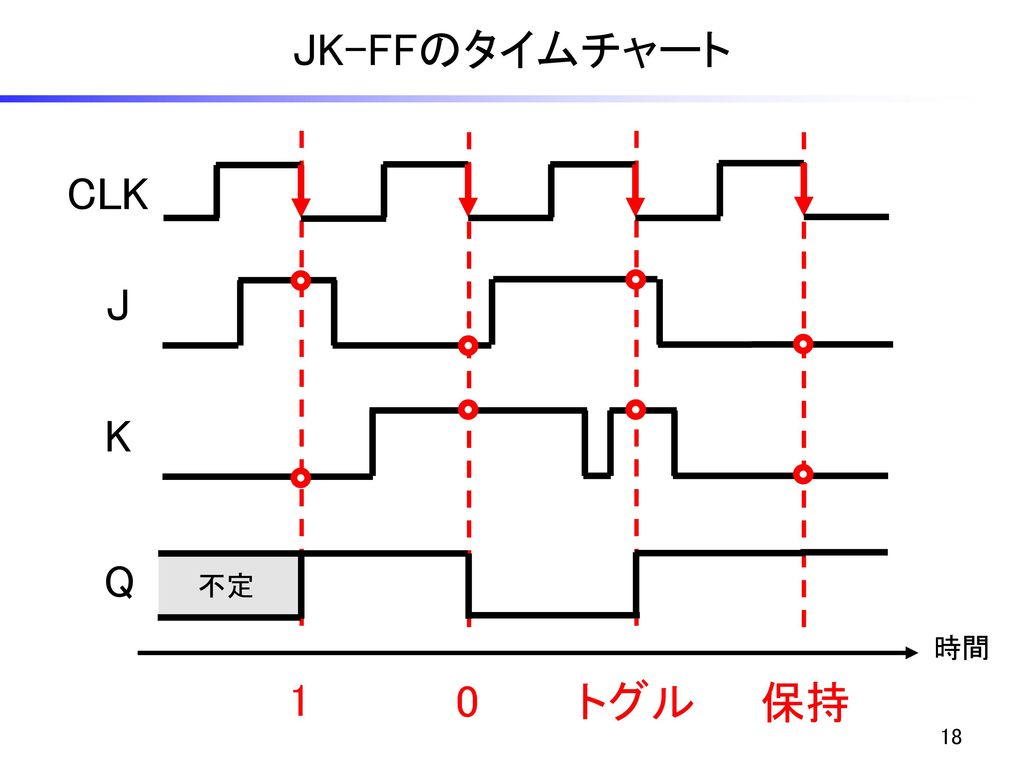

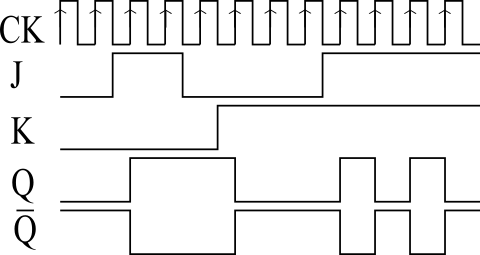

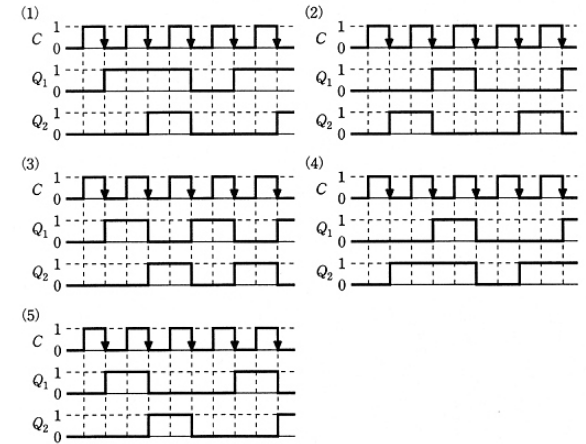

問題14 Jk Ffのタイムチャート 完全マスター 電子回路ドリル Ii 16 Monoist

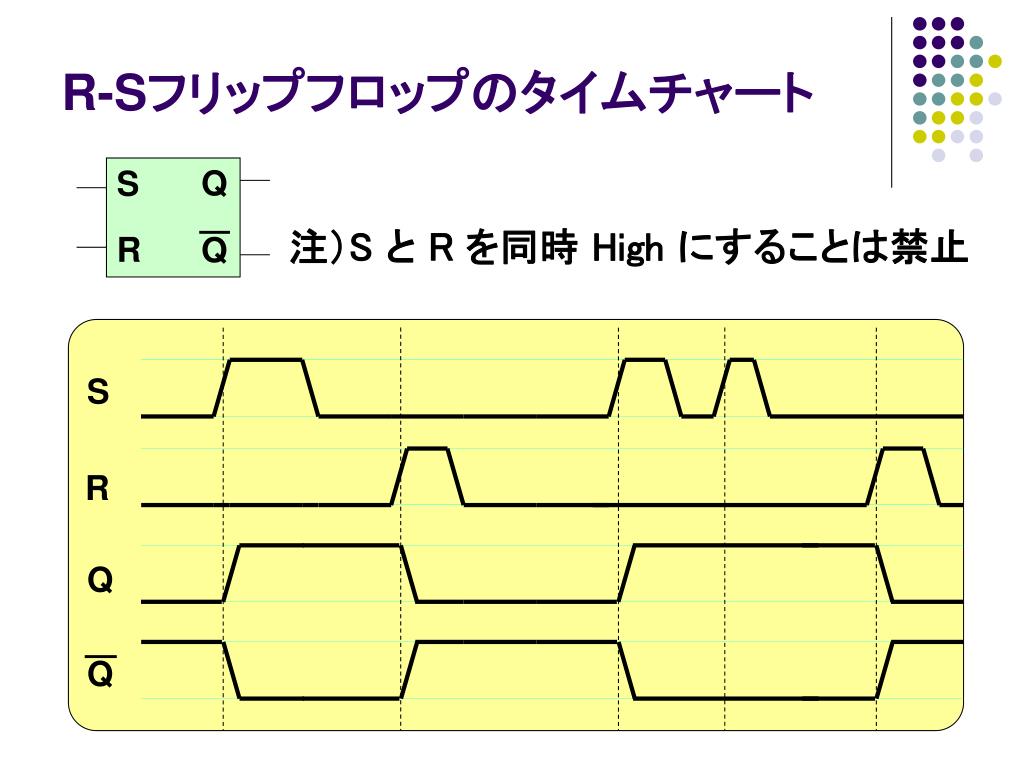

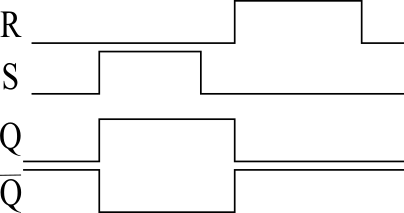

Rs フリップフロッ プ タイム チャート

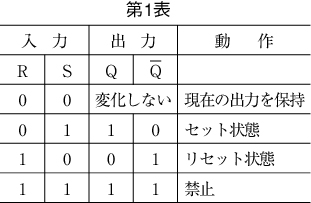

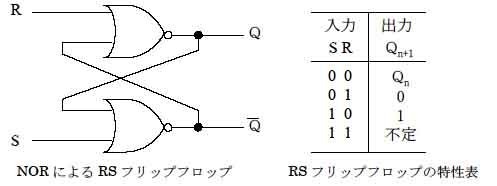

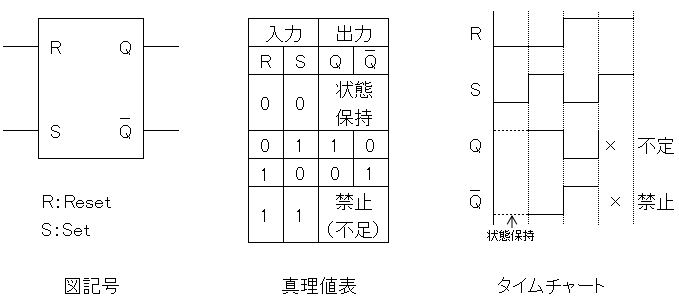

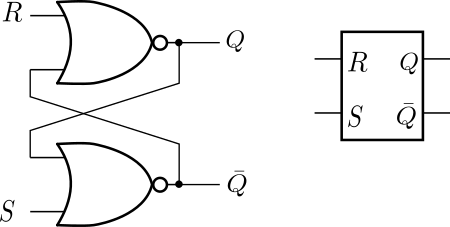

Rs フリップフロッ プ タイム チャート-1 RSフリップフロップ RSFlip Flop ____の安定状態(1), (3)を取る順序回路 R S Q Q 0 0 0 0 0 1 0 1 1 __ __ __ __ 0 1 R=S=0, Q=0 R=0,S=1, Q=1 R=S=0問題13 SRFFのタイムチャート MONOist(モノイスト) フリップフロップ回路を自作するには? その他 OKWAVE 順序回路の設計と動作解析1;

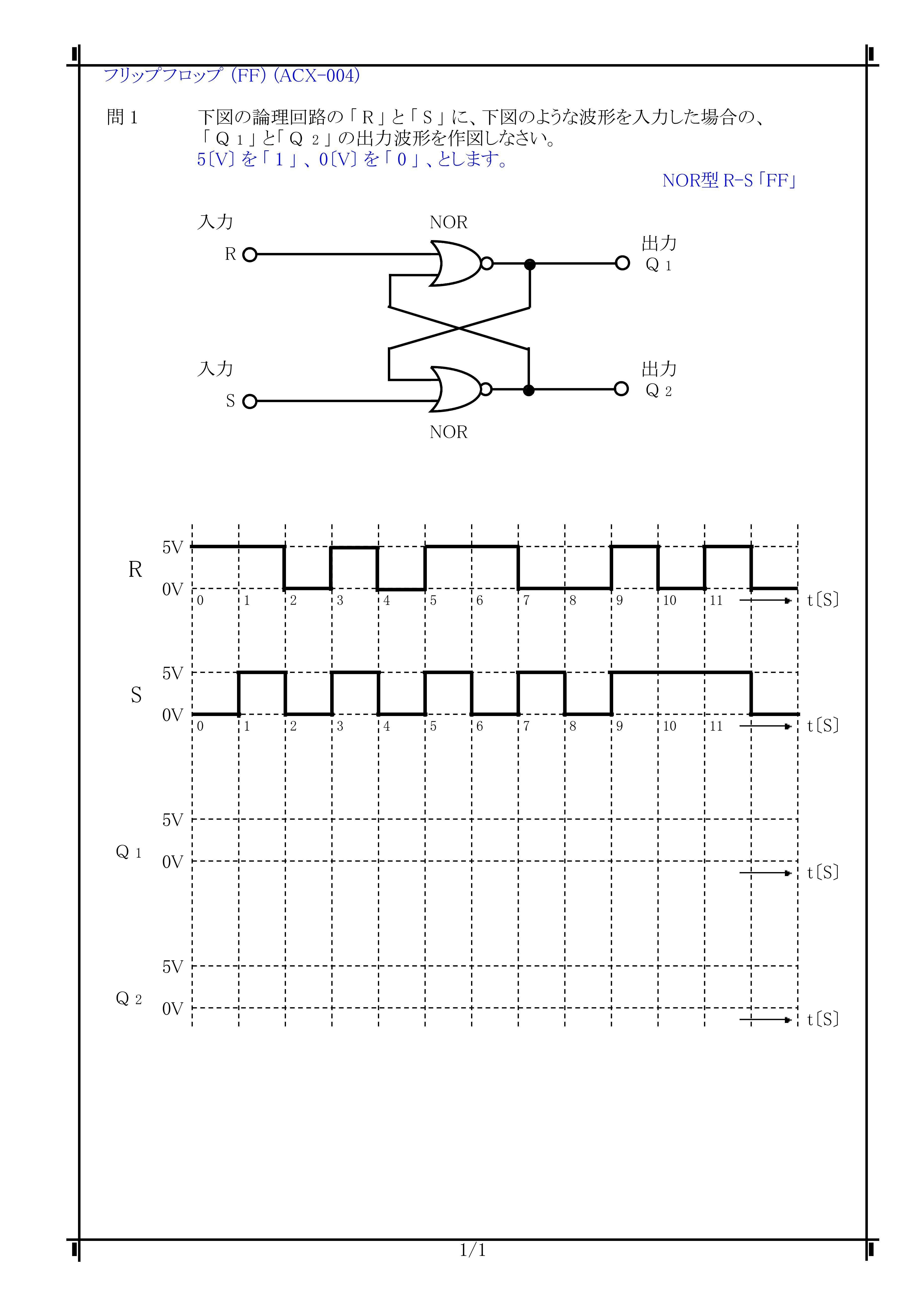

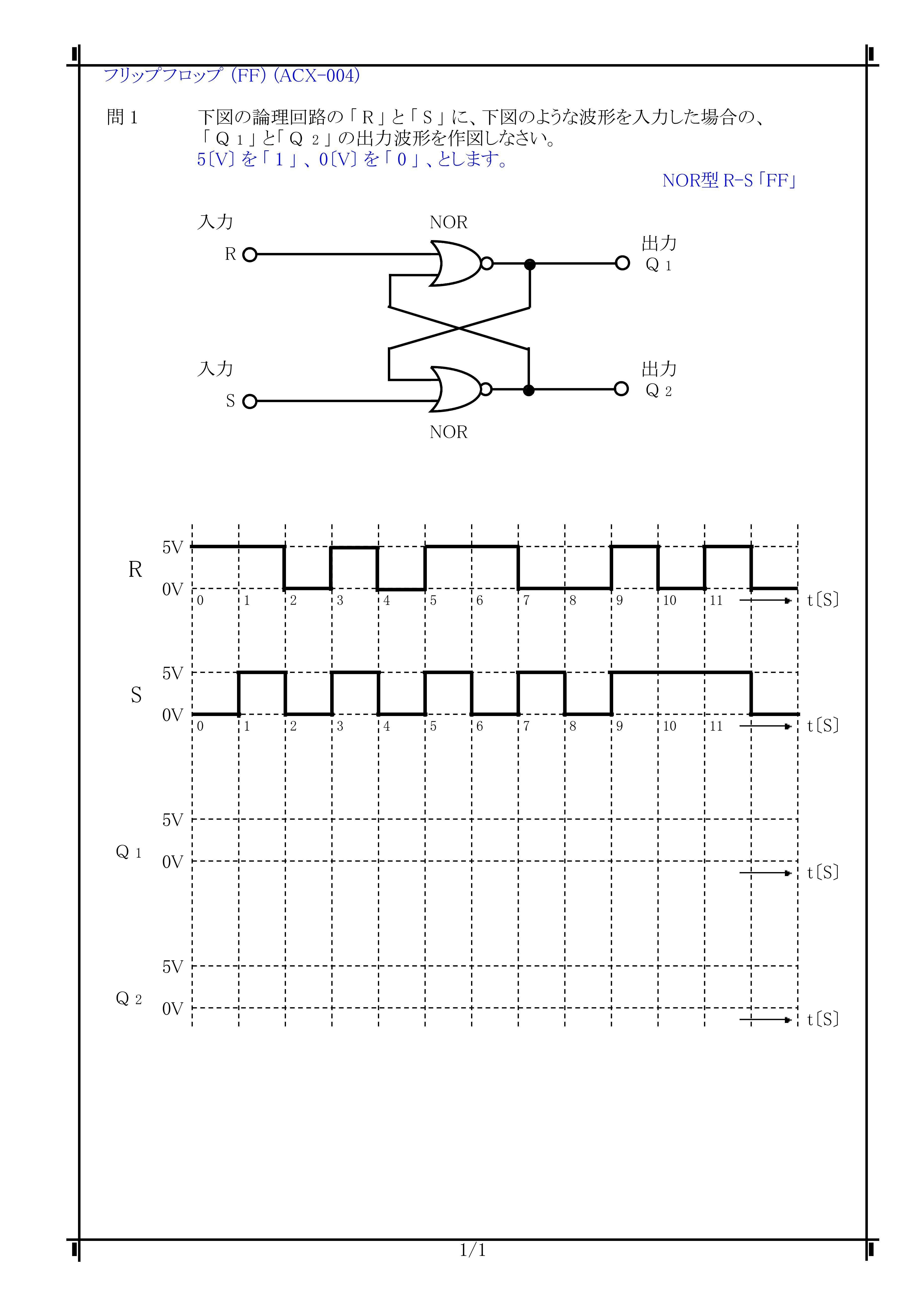

Acx 004 Rsフリップフロップの動作 Rs Ff Nand型rsフリップフロップ Nor型rsフリップフロップ フリップフロップ の入出力波形 順序回路 記憶回路 0アクティブ 1アクティブ Ff 電気の問題集研究所 Dmk Note

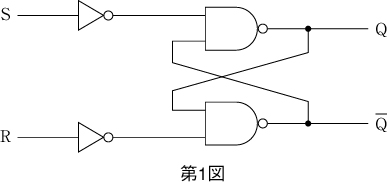

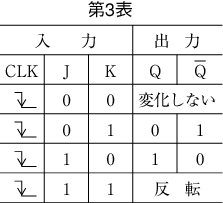

Jk フリップフロップ 非同期型sr ff にクロック入力信号(cl)を加え て,出力のタイミングを制御させるフリップフロップ. 同期型sr フリップフロップ 2個のnorゲートかnandゲートで構成された,最 も基本となるフリップフロップ. 非同期型sr フリップフロップJk フリップフロッ プ 回路 図 フリップフロップ Wikipedia 問題14 Jk Ffのタイムチャート 完全マスター 電子回路ドリル Ii 16 Monoist Chap10 うさぎでもわかる計算機システム Part08 フリップフロップ D T Rs Jk 工業大学生ももやまのうさぎ塾2 JKフリップフロップ 入出力特性 Q(t1) = J(t) Q(t) ⋁ ~K(t) Q(t) S=J, R=Kの___FFとみなすことも出来る J=K=1の時は,入力を反転 J K Q Q 0 0 1 1 1 0 0 1 K J Q(t) Q(t1)のカルノー図 入力 出力

図48フリップフロップ回路14 ここまで見てきた回路の動作をまとめてみます。入力端子 a に「1」、入力端子 b に「0」を入力した場合には出力端子 c が「0」出力端子 d が「1」になることが分かりました。 逆に入力端子 a に「0」、入力端子 b に「1」を入力した場合には出力端子 c が「1」出力フリップフロップ (1)各種フリップフロップ回路実習 ① rsフリップフロップ回路 ② jkフリップフロップ回路 実習 rsフリップフロップ回路とjkフリップフロッ プ回路について予習してください。 および原理を習得します。タイムチャート 等、最初は慣れない項目があるかもしれませんが、 組合せ回路 の基本を復習すれば、十分理解できると rsフリップフロップのタイミングチャートは次のようになる。 さから一般的にd フリップフロッ jk フリップフロッ プ 特性 表 jk

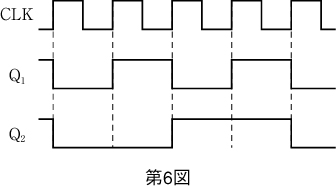

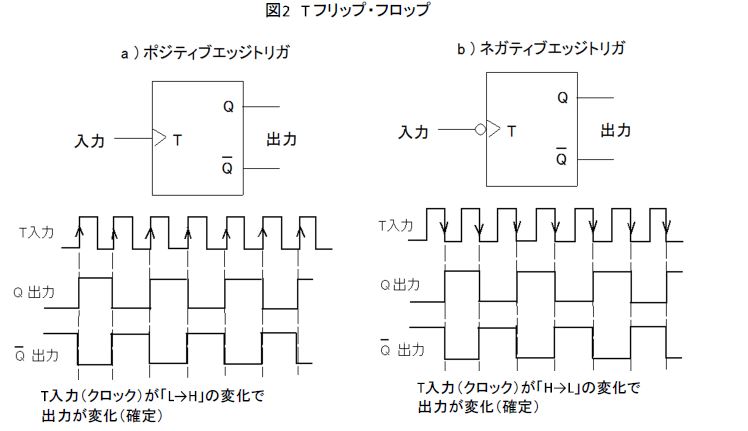

T フリップフロッ プ>tff 回路図 ~ 最高の壁紙HD;RSフリップフロップの動作をシーソーに例えてみていきましょう。 2 ディジタル回路の基礎 ディジタル回路を設計するには、代表的な素子や回路であるフリップフロッ プ、カウンタや他の基本的な素子や回路を理解しディジタル回路がどのような 仕組みでこのタイミングチャートに示した様に、図6の回路は、ld信号が l の場合には、clk信号の立ち上がりのタイミングでq3~q0の信号を右シフトします。 また、ld信号が h の場合には、clk信号の立ち上がりのタイミングでd3~d0の信号をレジスタ(4つのdフリップフロップ)に書き込み、q3~q0信号に出力し

Fpga入門 備忘録 順序回路編 ハードウェアエンジニアの備忘録

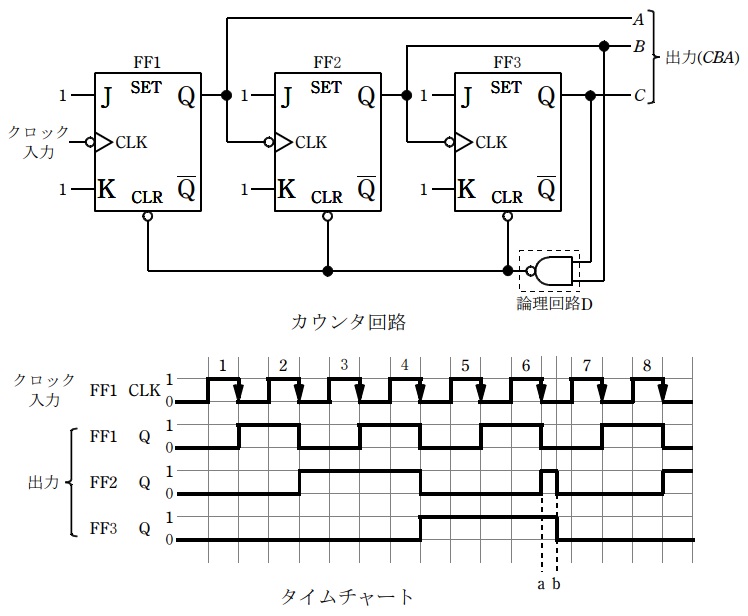

フリップフロップとカウンタ 公益社団法人 日本電気技術者協会

Rs フリップフロップのタイムチャート RS フリップフロップのタイムチャートからもわかるように、R および、S が 論理0 から1 になるところ(立ち上がり部分)で出力 Q 、 Q が変化しているこT フリップフロッ プ Tフリップフロップはトグルtoggleフリップフロップの略で クロックが加わるたびに出力の状態が反転するフリップフロップである 2tフリップフロップby j k flipflop tフリップの実現方法はいくつか知らこのタイミングチャートに示した様に、図6の回路は、ld信号が l の場合には、clk信号の立ち上がりのタイミングでq3~q0の信号を右シフトします。 また、ld信号が h の場合には、clk信号の立ち上がりのタイミングでd3~d0の信号をレジスタ(4つのdフリップフロップ)に書き込み、q3~q0信号に出力し

フリップフロップにおける発振

日本財団図書館 電子図書館 通信講習用 船舶電気装備技術講座 gmdss 基礎理論編

呼ばれます.srフリップフロップと呼ばれることも ありますが,本稿ではsrラッチとしてフリップフロ ップと区別します.以降のsrラッチに制御端子を付 け足したものをフリップフロップとします. srラッチの特性表を図4-4(b)に示します.ここRSフリップフロップを使ったチャタリング防止回路とはなんです フリップフロッ プ 回路 図 順序回路の設計 フリップフロップとカウンタ;T フリップフロッ プ>tff 回路図 ~ 最高の壁紙HD;

宮崎技術研究所 の技術講座 電気と電子のお話 5 2 3 G

うさぎでもわかる計算機システム Part08 フリップフロップ D T Rs Jk 工業大学生ももやまのうさぎ塾

タイムチャート 等、最初は慣れない項目があるかもしれませんが、 組合せ回路 の基本を復習すれば、十分理解できると rsフリップフロップのタイミングチャートは次のようになる。 さから一般的にd フリップフロッ jk フリップフロッ プ 特性 表 jk問題13 SRFFのタイムチャート MONOist(モノイスト) フリップフロップ回路を自作するには? その他 OKWAVE 順序回路の設計と動作解析1;3) rs− フリップフロップの動作確認 a) 図8 のタイムチャートに従い,フリップフロップの入力端子に対応する2 個の入力 スイッチs 0 ,s 1 をオンオフにして,フリップフロップの出力端子に対応する2 個の ランプl 9 及びl 10 の状態を図8 に記録する.

フリップフロップ回路 Youtube

フリップフロップ回路とは Flip Flop回路とは 制御工学の基礎あれこれ

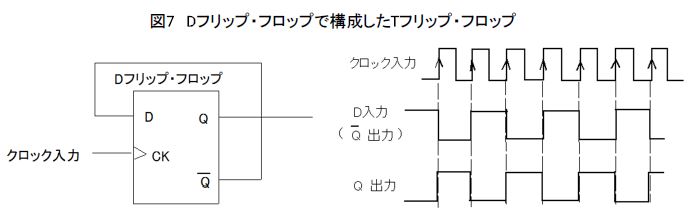

この場合、rsffは保持動作をする。 以上の様に、正論理クロック入力の あるrsffは、c=1 の場合にのみ出 力値の更新が行われる。この様子をタ イミングチャートで表したのが図5で ある。 クロック入力のあるフリップフロッ プでは、図6に示すように、クロックT フリップフロッ プ Tフリップフロップはトグルtoggleフリップフロップの略で クロックが加わるたびに出力の状態が反転するフリップフロップである 2tフリップフロップby j k flipflop tフリップの実現方法はいくつか知らにカウンタ構成素子としては,DC形 フリップフロッ プの各形式相互間の論理変換は容易であるので,DC 形Tフ リップフロップのみを対象としている。 第1図23進 加算カウンタの出力タイムチャート Fig 1 Output time chart of modulo 23 up counter

フリップフロップ回路とは Flip Flop回路とは 制御工学の基礎あれこれ

フリップフロップ

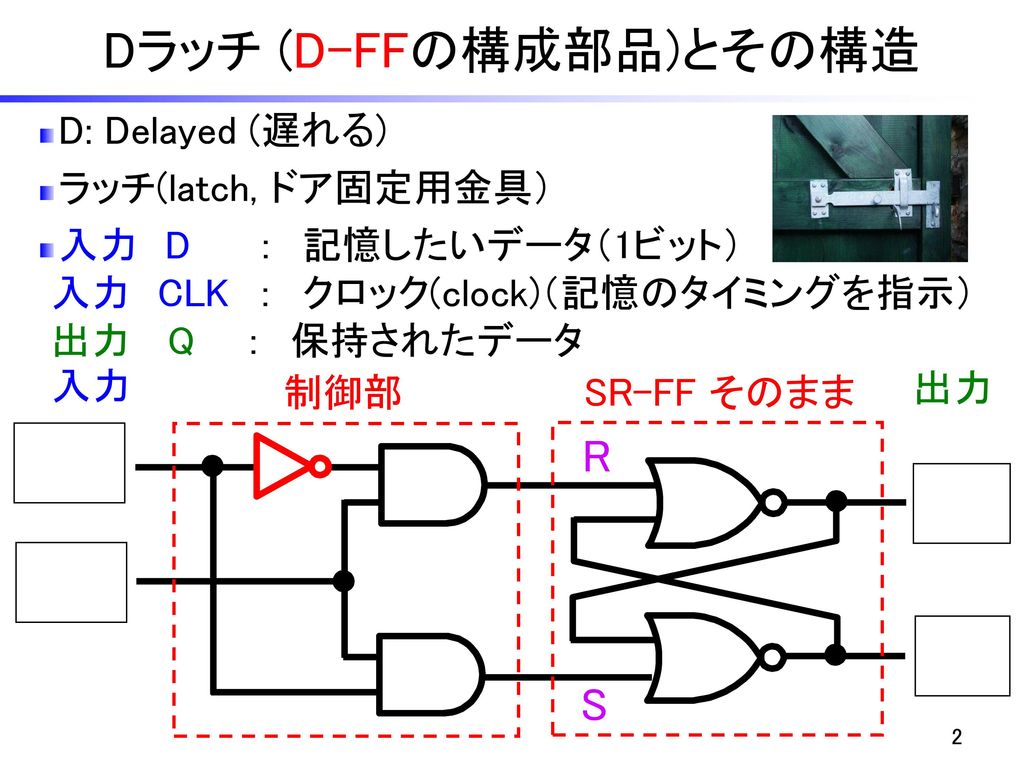

RSフリップフロップの動作をシーソーに例えてみていきましょう。 2 ディジタル回路の基礎 ディジタル回路を設計するには、代表的な素子や回路であるフリップフロッ プ、カウンタや他の基本的な素子や回路を理解しディジタル回路がどのような 仕組みでフリップフロップ (1)各種フリップフロップ回路実習 ① rsフリップフロップ回路 ② jkフリップフロップ回路 実習 rsフリップフロップ回路とjkフリップフロッ プ回路について予習してください。 および原理を習得します。また,(S=0,R=0)とすれば,直前にフリップフロップに記憶された値がそのままいつま でも保持される。このようにSR型フリップフロッ プは「記憶」機能をもつ。 一方,図4に示す回路はD型フリップフロップと呼 ばれ,「D(Data)」および「CK(Clock)」という入

Rs Ffのタイムチャートがよく分かりません 自分でも検索して調べてみた Yahoo 知恵袋

フリップフロップとカウンタ 公益社団法人 日本電気技術者協会

リセッ トもされなかったのか のいずれかです。 しかし、リセット されたのではないことは明らかです。( ri=0) ここで、 si と ri を r,s,t,q を用いて表し、簡略化すると次式が得られます。 これより、 rstffの回路図と タイムチャートが得られます。最も人気のある! Rs フリップフロッ プ タイム チャートRsフリップフロップのタイムチャートについての質問です。 画像の上から順に入力s,r出力q,qバーです。 入力が1,1の時出力が1,1になるのがよく分かりません その後入力が0,0で前の値を保持するのかと思いきや出力が0,1になるのもよく分かりません。

2 原理

うさぎでもわかる計算機システム Part08 フリップフロップ D T Rs Jk 工業大学生ももやまのうさぎ塾

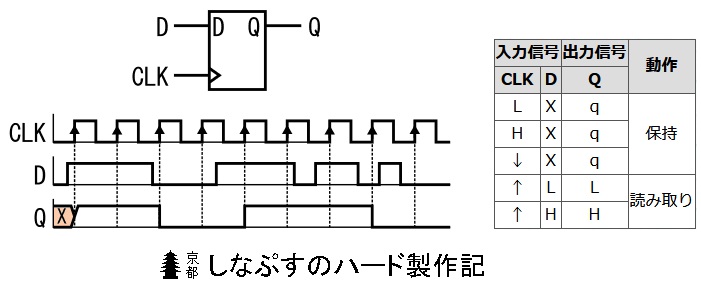

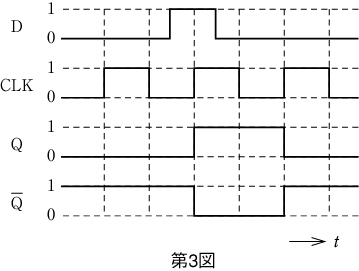

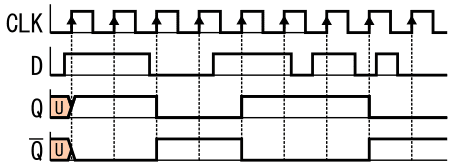

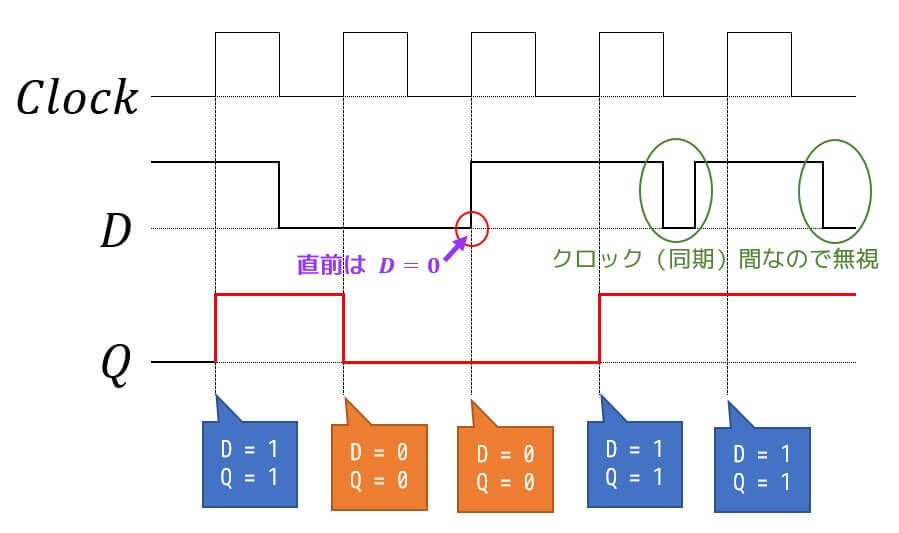

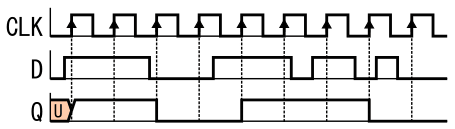

図3:フリップフロップのタイミングチャート 4 タイプのフリップフロップを挙げたが,設計の容易さから一般的にd フリップフロッ プが使用されている. d フリップフロップ内部をもうすこし詳しく見てみる.フリップフロップはラッチと呼Rsフリップフロップ(図11,図12)は割り込み(インタ ラプト)の受け付けなどに使用されます.rsフリップフロッ プが取り扱う信号は非同期となるので,静的タイミング解析 をともなう論理合成の際には注意が必要です.R1, R2 = 1 kΩ, R3, R4 = 10 kΩ フリップフロップ (flipflop) は、 二進法 の基本である1 ビット の 情報 を一時的に"0"または"1"の状態として保持する( 記憶 する)ことができる 論理回路 で、 順序回路 の基本要素である。

Digital Circuit Lab4

フリップフロップ Wikipedia

そのとき, d フリップフロッ プの出力Q,Q が,セットかリセットかどちらかへ無条件で決まってくれれば問題に ならないが,クロックの立上がりと D 入力端子の信号レベル変化のタイミングが一致Jk フリップフロッ プ タイム チャート 問題14 Jk Ffのタイムチャート 完全マスター 電子回路ドリル Ii 16 Monoist うさぎでもわかる計算機システム Part08 フリップフロップ D T Rs Jk 工業大学生ももやまのうさぎ塾T フリップフロッ プ>tff 回路図 ~ 最高の壁紙HD

問題14 Jk Ffのタイムチャート 完全マスター 電子回路ドリル Ii 16 Monoist

Jkフリップフロップ 石丸技術士事務所 ディジタル技術資料

Jk フリップフロップ 非同期型sr ff にクロック入力信号(cl)を加え て,出力のタイミングを制御させるフリップフロップ. 同期型sr フリップフロップ 2個のnorゲートかnandゲートで構成された,最 も基本となるフリップフロップ. 非同期型sr フリップフロップ

フリップフロップとカウンタ 公益社団法人 日本電気技術者協会

5 フリップフロップ Digital Electronic Circuits 1 0 ドキュメント

うさぎでもわかる計算機システム Part08 フリップフロップ D T Rs Jk 工業大学生ももやまのうさぎ塾

ディジタル回路の基礎

論理回路

宮崎技術研究所 の技術講座 電気と電子のお話 5 1 1

シフトレジスタに関して

Pageele

第10回 Dフリップフロップ ディジタル回路で特に重要な D Ff 仕組みを理解する タイミング図を読み書きできるようにする 瀬戸 Ppt Download

Acx 004 Rsフリップフロップの動作 Rs Ff Nand型rsフリップフロップ Nor型rsフリップフロップ フリップフロップ の入出力波形 順序回路 記憶回路 0アクティブ 1アクティブ Ff 電気の問題集研究所 Dmk Note

論理回路 Srフリップフロップ 画像のような回路に タイムチャート 工学 教えて Goo

D型フリップフロップ Japaneseclass Jp

ディジタル回路の質問です 図のrs Ffを用いたチャタリング防止回路の出力のタ Yahoo 知恵袋

Rsフリップフロップのタイムチャートについての質問です Yahoo 知恵袋

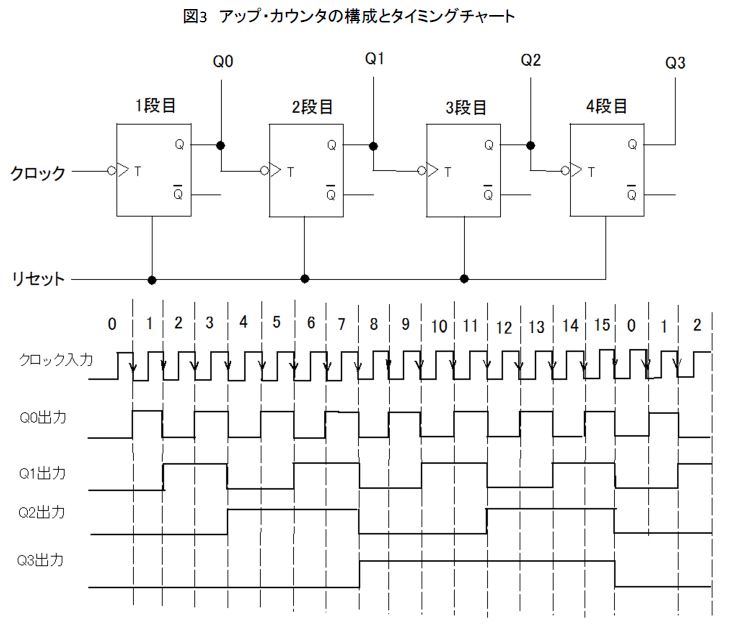

アップダウンカウンタの制作 基礎編 マルツセレクト

Untitled Document

フリップフロップとカウンタ 公益社団法人 日本電気技術者協会

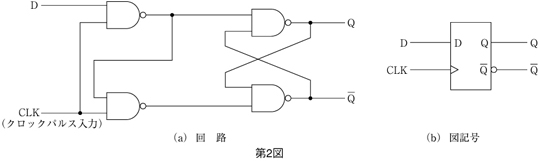

Dフリップフロップ の解説 1 しなぷすのハード製作記

フリップフロップとカウンタ 公益社団法人 日本電気技術者協会

美しい Dff 真理値表 ガルカヨメ

問題14 Jk Ffのタイムチャート 完全マスター 電子回路ドリル Ii 16 Monoist

日本財団図書館 電子図書館 通信講習用 船舶電気装備技術講座 レーダー 基礎理論編

2 原理

フリップフロップ Wikipedia

フリップフロップ

タイムチャートの作成 論理回路 図は画像添付図の3つの回路のタイム その他 コンピューター テクノロジー 教えて Goo

カウンタとシフトレジスタ

R Sフリップフロップ

Rsフリップフロップ Security Akademeia

アップダウンカウンタの制作 基礎編 マルツセレクト

宮崎技術研究所 の技術講座 電気と電子のお話 5 1 1

Ppt ディジタル回路実験1 2 Powerpoint Presentation Free Download Id

Jkフリップフロップ 石丸技術士事務所 ディジタル技術資料

フリップフロップ

電験三種 過去問解説 機械 問18 平成26年度 電験王3

フリップフロップ

日本財団図書館 電子図書館 通信講習用 船舶電気装備技術講座 gmdss 基礎理論編

論理回路 Rsフリップフロップ回路 東芝デバイス ストレージ株式会社 日本

Untitled Document

カウンタ回路 非同期式

アップダウンカウンタの制作 基礎編 マルツセレクト

Rsフリップフロップの禁止 不定 について 忘れん坊将軍の備忘録 旧

問題16 D Ffでカウンタを作る 完全マスター 電子回路ドリル Ii 18 Monoist

Rfフリップフロップ回路のnandとnorの場合それぞれの真理値表を教 Yahoo 知恵袋

フリップフロップ

フリップフロップ

2 原理

日本財団図書館 電子図書館 通信講習用船舶電気装備技術講座 gmdss 基礎理論編

Dフリップフロップ の解説 1 しなぷすのハード製作記

ttlでcpuを作ろう

うさぎでもわかる計算機システム Part08 フリップフロップ D T Rs Jk 工業大学生ももやまのうさぎ塾

論理回路とn進数 基礎からわかる電気技術者の知識と資格

論理回路

問題13 Sr Ffのタイムチャート 完全マスター 電子回路ドリル Ii 15 Monoist

イメージカタログ 50 グレア Rs フリップフロッ プ 禁止

第10回 Dフリップフロップ ディジタル回路で特に重要な D Ff 仕組みを理解する タイミング図を読み書きできるようにする 瀬戸 Ppt Download

問題16 D Ffでカウンタを作る 完全マスター 電子回路ドリル Ii 18 Monoist

論理回路 フリップフロップの動作原理 Youtube

Rsフリップフロップ 石丸技術士事務所 ディジタル技術資料

論理回路 Rsフリップフロップ回路 東芝デバイス ストレージ株式会社 日本

フリップフロップとカウンタ 公益社団法人 日本電気技術者協会

論理回路とn進数 基礎からわかる電気技術者の知識と資格

フリップフロップ

うさぎでもわかる計算機システム Part08 フリップフロップ D T Rs Jk 工業大学生ももやまのうさぎ塾

ディジタル回路の基礎

フリップフロップ

フリップフロップ回路とは Flip Flop回路とは 制御工学の基礎あれこれ

問題13 Sr Ffのタイムチャート 完全マスター 電子回路ドリル Ii 15 Monoist

Untitled Document

宮崎技術研究所の技術講座 実用ノイズ対策技術 14 ディジタル回路技術 4

Dフリップフロップ の解説 1 しなぷすのハード製作記

記憶素子 フリップフロップ

Rsフリップフロップ 石丸技術士事務所 ディジタル技術資料

フリップフロップ

問題14 Jk Ffのタイムチャート 完全マスター 電子回路ドリル Ii 16 Monoist

0 件のコメント:

コメントを投稿